# 90C701 for Advanced Communication Systems

## Preview - November 1995

#### TEMIC / MATRA MHS FAX-IT We Want Your Comments

#### FAX (+33) 1-30 60 71 57 e-mail : c701.preview@matramhs.fr

TEMIC / MATRA MHS SPARClet<sup>TM</sup> Applications Engineering provides a Fax number and an e-mail address for your comments about the content of the Advanced Communication Controller 90C701 Preview. We welcome your suggestions.

When referring to items in the preview, please reference the section number, page number, line number, and, if applicable, figure number and table number.

When sending a FAX or e-mail, please provide your name, company name, FAX number, and phone number.

The information contained herein is subject to change without notice. No responsibility is assumed by MATRA MHS SA for using this publication and/or circuits described herein: nor for any possible infringements of patents or other rights of third parties which may result from its use.

## **About this Preview**

The 90C701 is the first in the SPARClet<sup>TM</sup> microcontrollers family and provides the basis for developing further derivative compatible products already forecasted.

The goal of this preview is to define the features and functionality of the 90C701 microcontroller for project leaders, system architects, hardware and software designers. The 90C701 preview has been organized accordingly. This document is composed of three main chapters:

#### Chapter I: Product Overview

The product overview lists the main features of the product without going to detailed functionality.

#### Chapter II: Product Architecture

The product architecture chapter includes the sections called "SPARClet<sup>™</sup> Architecture" and "The 90C701 as a SPARClet<sup>™</sup> Implementation". Main SPARClet<sup>™</sup> implementation dependant features are described.

#### **Chapter III : Product Description**

The product description chapter is organized around the "90C701 Programming Model" and the "90C701 Operations and Registers Description" sections. These two parts give a detailed information on memory organization, instructions set, registers organization and associated operations.

The following additional reading are suggested.

- The SPARC Architecture Manual Version 8, SPARC International, Inc.

- SPARC-V8 Embedded (V8E) Release 1 Architecture Specification.

This can provide background to the information in this preview.

## Table of Content

page

| Chapter I Product Overview                               |     |

|----------------------------------------------------------|-----|

| 1 90C701 Microcontroller Overview                        | . 7 |

| 1.1 The CPU Core                                         | . 7 |

| 1.2 The Core Bus                                         | . 8 |

| 1.3 Bus Interface & Debug Support                        |     |

| 1.4 On-Chip Peripherals                                  |     |

| 1.5 Features                                             |     |

| Chapter II Product Architecture                          |     |

| 2 SPARClet <sup>TM</sup> Architecture                    | 11  |

| 2.1 Performance Challenge                                |     |

| 2.1.1 Cycle Per Instruction (CPI)                        |     |

| 2.1.2 Instructions Per Task (IPT)                        |     |

| 2.2 Operating System Support                             |     |

| 3 The 90C701 as a SPARClet <sup>™</sup> Implementation   |     |

| 3.1 The 90C701 CPU Core                                  |     |

|                                                          |     |

| 3.1.1 Resource Conflicts                                 |     |

| 3.1.2 Execution Units                                    |     |

| 3.1.3 Load/Store Unit                                    |     |

| 3.1.4 Arithmetic and Logic Unit                          |     |

| 3.1.5 Communication Coprocessor                          |     |

| 3.1.6 Instruction Cache                                  |     |

| 3.1.7 Data Cache                                         |     |

| 3.2 The 90C701 Core Bus                                  |     |

| 3.3 90C701 On-Chip Peripherals                           |     |

| 3.3.1 Bus Interface Controller (BIC)                     |     |

| 3.3.2 PCM/USART                                          |     |

| 3.3.3 General Purpose Timer                              |     |

| 3.3.4 OS Timers                                          |     |

| 3.3.5 Watchdog                                           |     |

| 3.3.6 Peripheral Interface Adapter (PIA)                 | 28  |

| Chapter III Product Description                          |     |

| 4 90C701 Programming Model                               | 31  |

| 4.1 SPARC Compliance                                     | 31  |

| 4.1.1 The 90C701 and the SPARC V8                        | 31  |

| 4.1.2 The 90C701 and the SPARC V8 Complement - SPARC V8E | 31  |

| 4.2 Memory Organization                                  | 32  |

| 4.2.1 System Control Segment (SCS)                       | 32  |

| 4.2.2 Input/Output Segment (IOS)                         | 33  |

| 4.2.3 Not Cacheable Memory Segment (NCMS)                | 34  |

| 4.2.4 Cacheable Memory Segment (CMS)                     |     |

| 4.2.5 Logical to Physical MIOS Addresses Translation     |     |

| 4.3 Data Types and Alignment                             |     |

| 4.4 Registers                                            |     |

| -                                                        |     |

| 4.4.2 Ancillary State Registers (ASRs)                   |     |

| 4.5 Branching Control                                    |     |

| 4.6 Interrupts, Traps, and Exceptions                    |     |

| 4.7 90C701 Additional Instructions                       |     |

|                                                          |     |

## Table of Content

| pag                                                      | ge |

|----------------------------------------------------------|----|

| 4.7.1 SCAN instruction 4                                 | 46 |

| 4.7.2 SHUFFLE instruction 4                              | 17 |

| 4.7.3 MAC instructions 4                                 | 48 |

| 4.7.4 CPRDCXT / CPWRCXT: Read / Write an Communication 4 | 19 |

| Coprocessor Context Register                             |    |

| 4.7.5 CPPUSH[a] :                                        | 50 |

| 4.7.6 CPPULL 5                                           | 51 |

| 4.7.7 CBccc                                              | 52 |

| 5 90C701 Operations and Register Description 5           | 53 |

| 5.1 Communication Coprocessor 5                          | 53 |

| 5.2 Bus Interface Controller 5                           | 55 |

| 5.3 PCM/USART                                            | 51 |

| 5.3.1 Register mapping 6                                 | 51 |

| 5.3.2 Transmitter section                                | 52 |

| 5.3.3 Receiver section                                   | 55 |

| 5.4 Real-Time and General Purpose Peripherals            | 56 |

| 5.4.1 Timers                                             | 56 |

| 5.4.2 Peripheral Interface adapter (PIA) 7               | 70 |

| 6 90C701 Pin Out                                         | 71 |

| 7 90C701 Basic Configuration 7                           | 73 |

## **List of Figures**

#### page

| *                                                                             | 0   |

|-------------------------------------------------------------------------------|-----|

| Figure 1. 90C701 block diagram                                                | . 7 |

| Figure 2. RISC instruction pipeline                                           | 11  |

| Figure 3. SPARClet <sup>TM</sup> instruction pipeline                         | 12  |

| Figure 4. SPARClet <sup>TM</sup> Pipeline Scheduling - dot product inner loop | 13  |

| Figure 5. 90C701 CPU Core                                                     | 15  |

| Figure 6. Core bus interconnection                                            | 24  |

| Figure 7. Example of interleaved transactions on core bus                     | 24  |

| Figure 8. 90C701 Bus Interface Controller                                     | 25  |

| Figure 9. Memory and I/O Addressing Space (MIOS)                              | 26  |

| Figure 10. PCM/USART Block Diagram                                            | 27  |

| Figure 11. Segment Organization                                               | 32  |

| Figure 12. System Control Segment                                             | 32  |

| Figure 13. Input/Output Segment                                               | 33  |

| Figure 14. Cacheable Memory Segment                                           | 34  |

| Figure 15. Logical to Physical MIOS Addresses Translation.                    | 35  |

| Figure 16. Alternate Window Registers                                         | 38  |

| Figure 17. Communication Coprocessor Block Diagram                            | 53  |

| Figure 18. DSEL and DBE timings when Addresses are not multiplexed            | 55  |

| Figure 19. DSEL and DBE timings when Addresses are multiplexed.               | 56  |

| Figure 20. 90C701 Basic Board Configuration                                   | 73  |

## List of Tables

| •                                                                                                 | age |

|---------------------------------------------------------------------------------------------------|-----|

| Table 1. Resource conflicts on register file fetch                                                |     |

| Table 2. Instruction Cache Features                                                               |     |

| Table 3. Instruction Cache Address Decoding                                                       |     |

| Table 4. Instruction Cache Tag Register                                                           |     |

| Table 5. LRU Support Register                                                                     |     |

| Table 6. Instruction Cache Control Register                                                       |     |

| Table 7. Instruction Cache Controller Address Decoding                                            | 19  |

| Table 8. Data Cache Features                                                                      |     |

| Table 9. Data Cache Address Decoding                                                              |     |

| Table 10. Data Cache Tag Register                                                                 | 21  |

| Table 11. Data Cache Control register (DCCR)                                                      |     |

| Table 12. Data Cache Controller Address Decoding                                                  | 22  |

| Table 13. Possible System Configurations                                                          | 26  |

| Table 14. 90C701 on-chip peripherals mapping                                                      | 33  |

| Table 15. 90C701 Processsor State Register (PSR)                                                  | 38  |

| Table 16. Implementation Extension Register (ASR17)                                               | 39  |

| Table 17. Performance Counting Register (ASR18)                                                   | 40  |

| Table 18. Fault Status Register (ASR21)                                                           | 40  |

| Table 19. Alternate Window Configuration Register (ASR22)                                         |     |

| Table 20. Coprocessor State Register                                                              |     |

| Table 21. Exception and Interrupt Request Priority and tt Values                                  |     |

| Table 22. 90C701 Interrupt sources                                                                |     |

| Table 23. 90701 Additional Instruction Set                                                        |     |

| Table 24. SCAN instruction                                                                        |     |

| Table 25. SHUFFLE instruction                                                                     |     |

| Table 26. MAC instructions                                                                        |     |

| Table 20. MINC instructions         Table 27. CPRDCXT / CPWRCXT Instruction Set                   |     |

| Table 28. CPPUSH[a] Instruction Set                                                               |     |

| Table 29. CPPULL Instruction Set                                                                  |     |

| Table 20.     CFT OLD instruction Set       Table 30.     CBccc Instruction Set                   |     |

| Table 30. Object mistration Set       Table 31. Device Control Register (DCR)                     |     |

| Table 31: Device Control Register (DER)       Table 32: Device Timing Control Register (DTCR)     |     |

| Table 32. Device Timing Control Register (DTCR)       Table 33. Refresh Register (RR)             |     |

| Table 33. Kenesh Kegister (KK)         Table 34. SpaceMap Register (SMR)                          |     |

| Table 34. Spacemap Register (SMR)       Table 35. PCM/USART registers.                            |     |

| Table 35. PCM/USART registers.         Table 36. PCM/USART register mapping                       |     |

|                                                                                                   |     |

| Table 37. Transmitter Command Register (TCR)         Table 28. Transmitter Source Desister (TCR)  |     |

| Table 38. Transmitter Sync Register (TSR)         Table 20. Transmitter Let a free Provide (TTR)  |     |

| Table 39. Transmitter Interface Register (TIR)         Table 40. Transmitter State Devices (TSTR) |     |

| Table 40. Transmitter Status Register (TSTR)                                                      |     |

| Table 41. Receiver Command Register (RCR)                                                         |     |

| Table 42. Receiver Synchronisation Register (RSR)                                                 |     |

| Table 43. Receiver Interface Register (RIR)                                                       |     |

| Table 44. Receiver Status Register (RSTR)                                                         |     |

| Table 45. Peripherals programming instructions                                                    |     |

| Table 46. Operating System Timer                                                                  |     |

| Table 47. Timer Input Handler Register (TIHR)                                                     |     |

| Table 48.    Shaper Register (TSHR)                                                               |     |

| Table 49.    PIA Command Register (PCR)                                                           | 70  |

**Chapter I**

## **Product Overview**

## 90C701 : Advanced Communication Controller

## 1 90C701 Microcontroller Overview

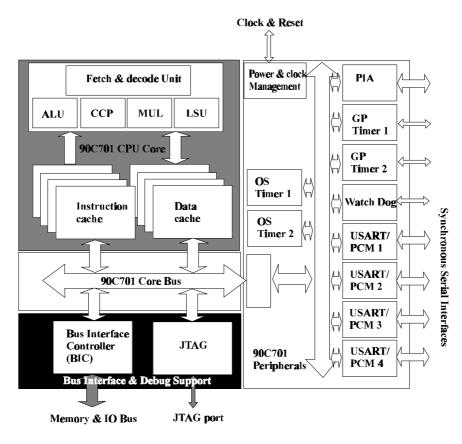

The 90C701 is an embedded SPARC processor with integrated communication peripherals. Built around a SPARClet<sup>TM</sup> CPU core, it includes the most frequently needed peripherals in advanced communication applications. The 90C701 is specially adapted for communication applications such as digital cellular base stations, bridges, routers, optical frame relay, ISDN adapters, and communication card controllers.

Figure 1. 90C701 block diagram

The 90C701 consists of a high-performance RISC fixed-point processor with integrated memories and devices controller, peripheral interface adapter, timers, USARTs, and JTAG port controllers.

### 1.1 The CPU Core

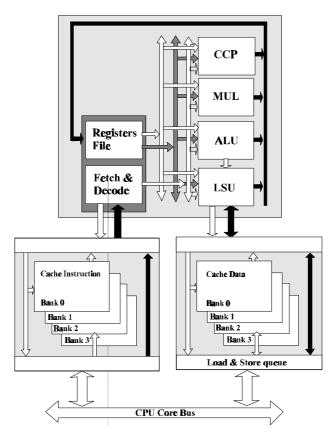

The CPU core integrates four execution units including a hardware multiplier (MUL), communication coprocessor (CCP), arithmetic and logic unit (ALU) and load-store unit (LSU). The 8 KB Data cache and 16 KB Instruction cache are integrated also and both use a four-way associative organization scheme. The CPU executes one instruction per cycle. Accordingly, all operations which require several cycles to be completed, are executed concurrently. For example, if the 90C701 is waiting for data coming back from the memory while the CPU is multiplying, both processing and transactions are done in parallel.

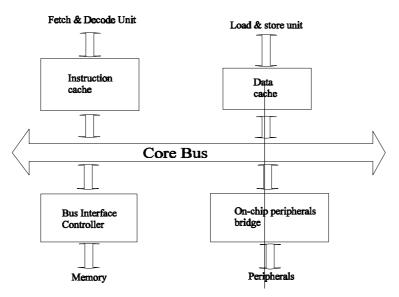

## **1.2 The Core Bus**

The 90C701 core bus is the main link between the instructions cache, the data cache, the I/O-memory interface units and the on-chip peripherals bridge. Using a split cycle bus protocol, each transaction is tagged and exploits the full bandwidth of the core bus, even in presence of wait states. According to the SPARClet<sup>™</sup> core bus protocol, the CPU performs the requests in order but the results comes back out of order.

## **1.3 Bus Interface & Debug Support**

The Bus Interface Controller (BIC) supports external I/O devices and memory banks of different speeds through a user-programmable interface. The I/O-memory bus is organized through a 32-bit data bus, addressing for 256 MB of external memory and peripheral devices. The 90C701 controls directly DRAM, SRAM, ROM and I/O devices in a 48 MB address space. The BIC supports also multimaster configuration.

Debug is supported by the JTAG port (IEEE 1149.1 compliant). This features a TAP (Test Access Port) which provides the support for accessing internal SPARClet  $^{TM}$  core bus agents as well as standard Boundary SCAN functions.

## **1.4 On-Chip Peripherals**

The 90C701 provides four synchronous-asynchronous serial interfaces. According to the available CPU load budget in the application, the transmission speeds can be in the range from 2 Mbits to 8 Mbits. For example, four transmissions at 2 Mbits can be achieved in full duplex, requiring only 30 % of the CPU load at 40 MHz. The physical interface of the serial port supports the PCM, UART, and USART signals, through a user-programmable interface.

Timers, Watchdog, and PIA are also on-chip peripherals. The OS Timers provide the time base to support the task and event scheduling activities of real-time operating systems. The General Purpose timers support several modes such as PWM (pulse width modulation). The Peripheral Interface Adapter (PIA) features up to 10 user-programmable general purpose input/output ports.

#### 1.5 Features

- Fully static SPARClet<sup>™</sup> CPU core

- On-chip clock frequency multiplier

- Industrial range operating frequency

- 30 MHz at 3.3V (+/- 10%)

- 50 MHz at 5V (+/- 10%)

- V8 compliant SPARC Processor

- Little & Big Endian data supported

- Transparent power management system

- Mulitply and Accumulate instruction

- Bit scanning and bit shuffling instructions

- 8 Register Windows

- Alternate Window Registers

- Instruction Cache

- 16 KBytes

- four-way associativity

- eight-words line size

- Lockable by bank

- Full LRU replacement algorithm

- Data Cache

- 8 KBytes

- four-way associativity

- four-words line size

- Lockable by bank

- Write through and copy back support

- Full LRU replacement algorithm

- 8 entries store buffer

- No write allocation

- Bus Interface Controller (BIC)

- 256 Mbytes address space

- DRAM interface with programmable refresh

- SRAM interface

- ROM interface

- Multimaster bus support

- 8-bit boot feature

- Control signals generated for 48 Mbytes.

- Communication Coprocessor (CCP)

- Coder/Decoder/CRC

- supported protocols : HDLC, V.110, proprietary

- 50 Mbit per second max. @ 50MHz

- Peripheral Interface Adapter

- 10-bit bidirectional port

- Lockable directions for secure design

- Timers

- 2 General Purpose Timers

- 2 Operating System Timers

- 1 Watchdog

- USART/PCMs

- 4 supported

- Distributed interrupt control logic

- software programmable interrupt levels

- JTAG with Boundary Scan

- 208-pin PQFP and 240-pin PGA packages

- 0.6 µm, 3 metal layers CMOS technology

# **Chapter II**

## **Product Architecture**

## **2** SPARClet<sup>™</sup> Architecture

The SPARClet<sup>™</sup> architecture is a SPARC V8 RISC based processor. Enhancements have been made to merge data processing and real-time control execution on the same cost-effective central processing unit. Combining parallel operational units and superscalar techniques, SPARClet <sup>™</sup> provides the best trade-off regarding the price/performance ratio.

SPARClet<sup>TM</sup> is particularly well adapted for emerging advanced communication systems which require high-performance embedded computing devices to support new applications such as real-time speech recognition or image processing. SPARClet<sup>TM</sup> is a general purpose architecture including Digital Signal Processing functions specially designed to address these requirements.

#### 2.1 Performance Challenge

The performance of a processor can be defined as the time required to accomplish a specific task and is expressed as the product of two factors:

## *Time per Task = CPI \* IPT*

CPI = Cycle Per Instruction

#### *IPT* = *Instruction per Task*

Performance can be improved by reducing any of these two factors. RISC-type designs strive to improve performance by minimizing the first factor. In the following sections, the SPARClet  $^{TM}$  advantage in these performance-related factors, is highlighted.

#### **2.1.1** Cycle Per Instruction (CPI)

One of the main benefits of using SPARClet<sup>™</sup> is its high performance/power consumption ratio (Mips/mWatt) as represented by the number of CPI (Cycles Per Instruction).

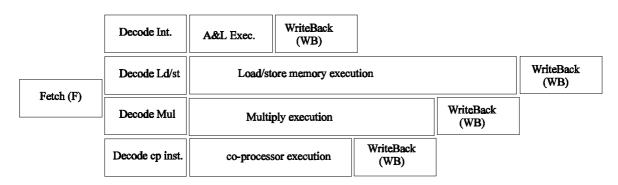

As with other RISC processors, SPARClet<sup>TM</sup> exploits the instruction pipeline and the load/store popular architecture. Accordingly, the SPARClet<sup>TM</sup> instruction pipeline works by dividing the execution of each instruction into four stages as shown in Figure 2 :

| Fetch (F)Decode (D)Execute (E)WriteBack (WB) |

|----------------------------------------------|

|----------------------------------------------|

Figure 2. RISC instruction pipeline

According to the RISC concept one instruction is fetched and decoded each cycle. However, enhancements have been made in the pipeline control to exploit the natural parallelism of the executed operations. In the SPARClet<sup>TM</sup> architecture all instructions requiring several cycles, such as multiply, load/store, and co-processor instructions, operate in parallel with the arithmetic and logic instructions. Accordingly, after the fetch stage the instruction is broadcast to the different execution units (including the fetch unit, which is responsible for control transfer instructions). Each execution unit is responsible for decoding, executing, and writing results in the register file. Consequently, results are written back out of order.

Figure 3. SPARClet<sup>™</sup> instruction pipeline

Load instructions read data from memory into processor registers for later processing by subsequent instructions. Because memory typically operates at much slower speeds than the processor, the loaded operand is not immediately available for subsequent instructions in a processor with an instruction pipeline. The technique used in many RISC designs to handle this data dependency is to rely on the compilers to handle the inherent latency and respect the load delay. Usually, to keep one CPI, the load delay must be one instruction. In SPARClet<sup>TM</sup> the latency or the duration of load delay covers the execution of several instructions.

Accordingly, the SPARClet<sup>™</sup> CPU needs one effective-cycle per instruction while traditional RISC based architecture will need 2 or 3 cycles in average to operate in applications. Wait states can be inserted for only two reasons : resource conflicts (a resource is already busy executing an operation and instruction needs it). and data dependencies (an instruction needs a data which is not yet available).

### **2.1.2** Instructions Per Task (IPT)

The number of executed instructions depends on the optimizing techniques used in compilers, such as register allocation, redundancy elimination, replacement algorithms with faster operation (Multiply-and-accumulate, bit shuffling or scanning), loop optimization, and pipeline scheduling. The SPARClet<sup>™</sup> architecture contributes to the reduction of instructions per task in two manners:

New instructions to support digital signal algorithms:

Multiply-and-accumulate instruction (MAC):

Accumulation is executed without an extra cycle. The speed of the MAC is the speed of the multiplier.

Bit scanning instruction (SCAN):

The SCAN instruction is particularly well suited to data normalization, priority encoding and run, length and coding algorithms. It replaces 30 scalar instructions.

Bit shuffling instruction (SHUFFLE):

The SHUFFLE instruction executes bit, couples, digits, byte, nibble, and half-word swapping, and supports efficiently the data endianess issue.

# Τεміс MATRA MHS

#### Pipeline scheduling:

In pipeline scheduling techniques the compilers schedule and reorganize instructions to ensure that pipeline delay slots are filled with useful instructions as illustrated earlier in the description of load delays.

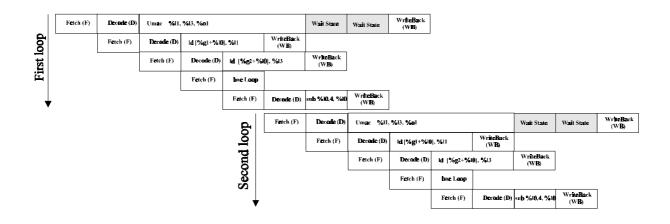

The following task (dot product) shows the benefit of the instruction reordering generated by the compiler. In this example, some of the 5 instructions in the inner loop require multiple cycles operations, such as the four-cycles latency Multiply-and-Accumulate (UMAC) instruction and the two-cycles latency Load (LD) instruction. A regular RISC processor will need 13 cycles to execute the loop. SPARClet<sup>™</sup> will do the same loop with only five cycles. Figure 4 shows the instruction scheduling for the inner loop of the dot product algorithm..

|       | [%g1+%l0], %l1 |       |     |          |        |       |

|-------|----------------|-------|-----|----------|--------|-------|

| Ia    | [%g2+%l0], %l3 |       |     |          |        |       |

| subcc | %10, 4, %10    |       |     |          |        |       |

| umac  | %ll, %l3, %ol  |       |     |          |        |       |

| ld    | [%g1+%l0], %l1 |       |     |          |        |       |

| ld    | [%g2+%l0], %l3 |       |     |          |        |       |

| bne   | Loop           |       |     |          |        |       |

| subcc | %10, 4, %10    | ; alw | ays | executed | (delay | slot) |

Figure 4. SPARClet<sup>™</sup> Pipeline Scheduling - dot product inner loop

In this example, the MAC instruction is ready to write back its result at the same time as load and subcc instructions. Two wait states have to be added to the MAC instruction to return the result to the register file. This resource conflict is described in the "Product Architecture" Chapter . Even with these two wait states, the SPARClet<sup>™</sup> architecture allows the processor to run at one CPI for this application.

### 2.2 Operating System Support

The performance gains obtained by providing support for operating systems are often subtle. The SPARClet<sup>™</sup> architecture supplies appropriate operating system support to enhance performance in this domain. For example SPARClet<sup>™</sup> supports Multiprocessor synchronization instructions. One of them performs an atomic read-then-set-memory operation; another performs an atomic exchange-register-with-memory operation. Enhancement has been done in order to provide fast trap handlers. In this domain extra features are supported by the SPARClet <sup>™</sup>, Single Vector Trapping and Alternate Window Registers. The interrupt response has been

#### Single Vector Trapping

Single vector trapping can spare code space. Due to the SVT, the traps table size is reduced from 4KB to four-words. After a trap has been taken, its Trap Type can be determined by reading the Trap Type field, *tt*, of the Trap Base Register (TBR). This can be used by software to determine subsequent processing of the trap.

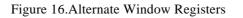

#### Alternate Window Registers

The Alternate Window Registers (AWR) consist of a separate set of 32 registers. The associated mechanism allows routines which manipulate large amounts of data (such as trap handlers or software direct memory access handlers) to switch context faster. This capability reduces the interrupt latency. Each level of interrupt (IRL) can be associated to alternate window registers or not. The alternate window registers avoid time loss in save/restore context operations.

Thanks to the SPARClet<sup>™</sup> architecture, another real-time improvement has been accomplished regarding the interrupt response time. The SPARClet <sup>™</sup> CPU can process an interrupt routine while it is executing memory loads/stores or multiplications. This characteristic allows a fast response time, as well as better determinism in the behavior of the real-time applications. The typical time from the interrupt detection (after de-glitching by the input handler in case of an external interrupt) to the trap handler's first instruction fetch is 6 to 7 clock cycles.

## **3** The 90C701 as a SPARClet<sup>™</sup> Implementation

### **3.1 The 90C701 CPU Core**

The 90C701 CPU core consists of two main subsystems, the control block and the execution units (Figure 5). The control block includes the Fetch and Decode unit and the three ports registers file and all the CPU control registers. The fetch and decode unit gathers all the sequencing functions.

Figure 5. 90C701 CPU Core

The register file is a triple port static RAM array. The 136 32-bit registers are divided into a set of 128 registers and a set of 8 global registers. The 128 registers are grouped into eight overlapping sets of 24 registers called register windows. Each window shares eight registers with its two adjacent windows. The Alternate Window Registers are an additional 32 registers window entered on specific conditions detailed in the "Product Description" Chapter.

The 90C701 CPU control registers include the Processor State Register (PSR), the Window Invalid Mask (WIM) register, the Trap Base Register (TBR), the Program Counters (PC, nPC), and the Ancillary State Registers (ASRs). A brief description of these registers is given in "Product Description" Chapter .

# 90C701

Four internal buses are used to control the execution units, while one bus is used by the control block to send the operation to the execution unit which will operate the decoded instruction. At the same time two buses are used to provide the two source operands to the associated execution unit. At this time the selected execution unit is responsible for the processing and the reporting activities of the instruction. Concurrent processing is fully supported by a dedicated hardware interlock mechanism which prevents any out-of-order data update. When the operation is completed, the execution unit writes back the result to the register file, sharing the destination bus with the other execution units.

Instructions are accessed by the processor from memory and are executed, annulled, or trapped. Instructions are encoded in three 32-bit formats and can be partitioned into five categories. The categories are the load/store instructions, the integer arithmetic instructions, the control-transfer instructions, Read/Write state registers, and Communication co-processor instructions. These instructions are presented in the next Chapter. These five instruction categories are implemented on four execution units which will be described below. These are the arithmetic and logic unit, the multiplier unit, the load/store unit, and the communication co-processor.

### **3.1.1** Resource Conflicts

In a running situation (as already discussed in the chapter SPARClet <sup>TM</sup> Architecture), wait states can be generated according to the resource conflict and/or to the data dependency. In most such cases, the compiler can use techniques such as instruction reordering to minimize the performance impact due to the data dependency between instructions.

Since the register file has only two read ports, some instructions, which need to access more than two operands in the same cycle, will generate wait states. The following table illustrates this situation.

| Operand fetch in register file | Instruction example  | Wait state |

|--------------------------------|----------------------|------------|

| no operand                     | bicc, sethi, cppull, | No         |

| rs1 only                       | add %r1, imm, %r2    | No         |

| rs1 and rs2                    | add %r1, %r2, %r3    | No         |

| rs1 and rd                     | st %r2,[%r1+imm]     | No         |

| rs1 and rd and rd+1            | std %r2,[%r1+imm]    | (*)        |

| rs1 and rs2 and rd             | st %r3,[%r1+%r2]     | (*)        |

| rs1 and rs2 and rd and rd+1    | std %r4,[%r1+%r2]    | (*)        |

Table 1. Resource conflicts on register file fetch

(\*) Note: These instructions generate wait state only if following instructions use the second read port of the register file.

Another source of conflict can be the write-back port of the register file. When the operation is completed, each execution unit will ask to access to this port to write its result in the registers file. In case of several write-back port requests during the same cycle, the execution units have to be prioritized according to instruction classes:

# TEMIC MATRA MHS

| Instruction class          | Priority |  |

|----------------------------|----------|--|

| Control-transfer           | 1        |  |

| Integer Arithmetic         | 2        |  |

| Load/store                 | 3        |  |

| Communication Co-processor | 4        |  |

| Multiplier                 | 5        |  |

Level 1 is the highest priority.

There are also possible conflicts within execution units, especially with the communication coprocessor, the multiplier, and the load/store units. In this case, the availability of the operators to execute the next operation is the main reason of wait states insertion.

#### **3.1.2** Execution Units

The execution units have been designed to support four classes of instructions. All run in parallel. The first class consists of instructions regarding external CPU accesses, such as load and store instructions, excepting the address generation. The second class is associated to the dedicated processing, such as multiplications, multiply-and-accumulate and read and write Y register. The third class, is specific to the 90C701 communication oriented co-processor instructions. The last class includes the traditional arithmetic and logic instructions : in other words, all the scalar instructions and the address generation function (JMPL, RETT, STORE, LOAD).

#### **3.1.3** Load/Store Unit

The load/store unit is in charge of all the transactions between the CPU core, the data cache, and memory-I/O external devices. The load/store unit can bufferize up to four ongoing loads once all information has been sent to the data cache while it is waiting for data to come back. The load instructions take one cycle to send an address. The store instructions can take from one to three cycles according to resource conflict cases as shown above.

#### **3.1.4** Arithmetic and Logical Unit

The ALU performs all integer arithmetic and logical instructions, which are generally triadic-register-address instructions. The ALU computes a result that is a function of two source operands, and either writes the result into the destination register r[rd] or discards it. One of the source operands is always r[rs1]. The other source operand depends on the *immediate operand bit* (*i*) in the instruction. If i=0, the operand is r[rs2], but if i=1, the operand is the constant simm13 sign-extended to a width of 32 bits. The ALU is also responsible for computing a 32-bit, byte-aligned memory address for the Load and store instructions.

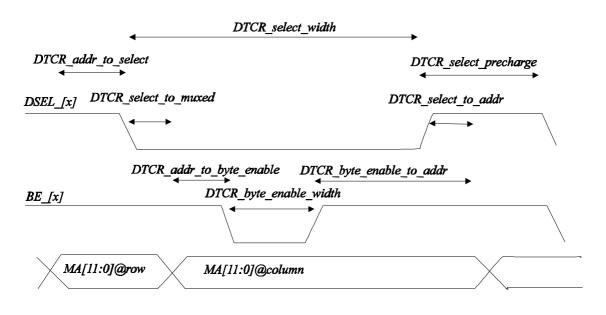

#### 3.1.5 Communication Coprocessor

The coprocessor supports HDLC and V110 communication protocols: they require the following functions:

- Coding messages, interleaving them with a byte granularity and transmitting the resulting bit stream on a serial interface.

- Receiving a bit stream from a serial interface, allocating its bytes to different messages and decoding them.

# 90C701

The coding and interleaving functions are executed by the communication coprocessor, as well as the reverse operations (decoding and byte allocation). It sustains a 1-bit per cycle throuput for medium size messages. Serial bit stream transmission and reception are handled by an on-chip PCM interface, capable to manage up to 8-Mb/sec full duplex data streams. Each PCM features 2 FIFO's of 12-Bytes each to smoothen transmission and reception processes.

Synchronization between the coprocessor and the PCM peripheral is ensured by an interrupt mechanism, with minimal context switching overhead, which supports 64-bit DMA transfers in less than 20 cycles. The Alternate Window (detailed in Chapter Product Description), provides the DMA pointers and counters for up to three full duplex channels.

Coding functions are user-programmable for both message modification ("zero" insertion or suppression) and CRC computation (polynomial coefficients). This allows to support several protocol families on the same silicon part. Real-time compromises (latency between consecutive DMA interrupts, versus DMA throuput) are under user's control: he can program the PCM FIFO's threshold for DMA interrupt generation. As a result, a 90C701 running at 50 MHz could manage a full duplex 4-Mb/sec HDLC stream, and keep 45 Mips available for additional users' needs.

#### **3.1.6** Instruction Cache

The Fetch and Decode Unit processes instructions at a maximal rate of one CPI. Therefore, the Instruction Cache is able to fetch the code with the same performance level, in order to maximise the global throughput of the core.

Therefore, the 16 Kbytes Instruction Cache is split in 4 banks, according to a set associative scheme. Up to 3 banks can be locked simultaneously, avoiding "miss penalty" for critical routines smaller than 4 Kbytes (which fits for most embedded applications, for example critical trap handlers). The Instruction Cache features are summarized in the following table.

| Feature                                 | Benefits                                 |  |  |

|-----------------------------------------|------------------------------------------|--|--|

| 16-bytes (4 banks *128 lines * 8 words) | Good trade-off for embedded applications |  |  |

| four-way associative                    | High hit rate                            |  |  |

| eight-words line size                   | Performance (bus traffic)                |  |  |

| Lockable by bank                        | Critical routines deterministic behavior |  |  |

| Least Recently Used (LRU)               | Performance                              |  |  |

| Table 2. Instruction Cache Features     |                                          |  |  |

#### **Address decoding**

The input address supplied by the Fetch and Decode Unit is decoded as follows :

| Table 3. Instructi | on Cache Addre | ess Decoding |

|--------------------|----------------|--------------|

|--------------------|----------------|--------------|

| 28-12       | 11-5        | 4-2         | 1-0 |

|-------------|-------------|-------------|-----|

| Tag Address | Line number | Word number | 0 0 |

A Tag register is associated with each line of each bank (512 tag registers overall for the Instruction Cache).

| Table 4. Instruction Cache Tag Register |   |   |  |

|-----------------------------------------|---|---|--|

| 18-2                                    | 1 | 0 |  |

| Tag Address                             | Р | V |  |

P : Privilege associated with the line (0:User, 1:Supervisor) V : Valid bit

If the 18 most significant bits of the input address bits matches with the Tag Address field of one out of the 512 Tag Registers, the required address is present in the cache (Cache Hit). Otherwise, the Load/Store Unit (LSU) will have to wait for the data to be accessed in external memory (Cache Miss).

#### LRU algorithm

In order to support the LRU algorithm, a register of 8 bits has been dedicated for each line.

| Table 5. LRU Support Register |     |     |     |  |  |  |  |  |

|-------------------------------|-----|-----|-----|--|--|--|--|--|

| 7-6                           | 5-4 | 3-2 | 1-0 |  |  |  |  |  |

| LRU                           |     |     | MRU |  |  |  |  |  |

For each line, it contains 4 fields showing the Least Recently Used to Most Recently Used Bank numbers order. For example "3120" in LRU register for line 3 means that line 3/bank 0 was used the most recently, then bank2, then bank1 and bank 3 was the Least Recently Used. When a line has to be reloaded (In case of a Cache Miss), the Least Recently Used bank will be updated from main memory.

All LRU control bytes have to be initialized at 0xe4 ("3210" in LRU register).

#### Lock mechanism

The lock status is controlled by a 3 bit Instruction Cache Control Register (ICCR) :

|             | Table                                                | 6. Instruction C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Cache Control |  |  |  |

|-------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|

|             |                                                      | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0             |  |  |  |

|             |                                                      | _lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _enable       |  |  |  |

| ICCR_enable | When set, the                                        | Instruction Ca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ache is enab  |  |  |  |

| ICCR_lock   | Defines which<br>0 : no                              | banks are loc<br>locked bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | cked :        |  |  |  |

|             | 1 : bank 3 is locked<br>2 : banks 3 and 2 are locked |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |  |  |  |

|             |                                                      | the state $3$ and $2$ and $1$ |               |  |  |  |

|             | Bank 0 is not                                        | lockable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |  |  |  |

#### Instruction Cache Controller Address Space

The Cache Tag registers, the LRU registers, and the Control register can be read or updated using regular Store instructions in Supervisor mode. The address given in operand should be formatted as follows :

Table 7. Instruction Cache Controller Address Decoding

| 31-19             | 18 | 17-16 | 15 | 14 | 13 | 12 | 11-5        | 4-2         | 1-0         |

|-------------------|----|-------|----|----|----|----|-------------|-------------|-------------|

| 1 100 000 000 000 | Op | Reg   | B3 | B2 | B1 | B0 | Line number | Word number | Byte number |

Bits 31-19 are the Cache Controller Base address, fixed as shown on the table.

The Op field tells if it is an update ("0") or a check ("1").In case of a check, the data value given in operand in the Store instruction will be compared to the checked register content and the operation will return a Bus Error if the values are different.

Reg shows which register is to be checked/updated :

00 : Control Reg 01 : Cache memory 10 : Cache Tag 11 : LRU register

B3..B0 : bank number (used for Cache Memory and Cache Tag). A "1" indicates that the corresponding bank is selected. Any combination is legal.

Line number : used for Cache Memory , LRU register and Cache Tag.

Word number : for Cache Memory, indicates which word in the selected line is to be checked/updated Byte number : for partial store, indicates which byte of the word is to be checked/updated (Used for Cache Memory and the Cache Tag).

#### 3.1.7 Data Cache

The Fetch and Decode Unit processes instructions at a maximal rate of one CPI. Therefore, the Data Cache can be accessed (read or written) once per clock cycle, to maximize the global throughput of the core. The 8Kbytes Data Cache is split in four banks, according to a set associative scheme. Up to three banks can be locked, avoiding "miss penalty" for critical sets of data (constant tables for example). The different Data Cache parameters are summarized in the following table.

| Advantage                                                |

|----------------------------------------------------------|

| Good trade-off for Embedded applications                 |

| Allows four different contexts to use the same data set. |

| Performance (bus traffic)                                |

| Performance/Real-Time support                            |

| Performance (bus traffic)                                |

| Real-Time support                                        |

| Performance                                              |

|                                                          |

Table 8. Data Cache Features

In addition to standard caching functionalities, the Data Cache provides transaction queues (for load and store requests), so that multiple transactions can be handled simultaneously. Responses to load requests do not necessarily come back in order, and may pass missing loads being processed. This ability is called "hit-under-miss".

To maximize the performance gain of this enhancement, the Fetch and Decode Unit can generate several Data Cache accesses and continue the processing flow without waiting for the Data Cache responses, as long as no data dependency between consecutive instructions occured.

To support the "hit-under-miss" mechanism, the Data Cache and the Integer Unit respectively include a Store Buffer (eight entries) and a Load Buffer (four entries). The associated benefit is a Data Cache half as big as the Instruction Cache, with negligible impact on "miss penalty".

As the Data Cache implementation is very similar with the Instruction Cache, we will limit the following description to the differences.

#### **Address Decoding**

The input address is decoded as follows :

| Table 9. | Data | Cache | Address | Decoding |

|----------|------|-------|---------|----------|

|----------|------|-------|---------|----------|

| 28-11       | 10-4        | 3-2         | 1-0         |

|-------------|-------------|-------------|-------------|

| Tag Address | Line number | Word number | Byte number |

The Tag registers (one per line of each bank) :

| Table 10.Data Cache Tag Register |   |   |   |   |  |  |  |  |

|----------------------------------|---|---|---|---|--|--|--|--|

| 22-4                             | 3 | 2 | 1 | 0 |  |  |  |  |

| Tag Address                      | D | F | Р | V |  |  |  |  |

D : Dirty line (line inconsistent with the memory content, happens when copy back is used and the update not done).

F : Full support (When this line has been allocated, the memory controller guaranteed that an error at the given address will never occur)

P : Privilege (0 for user)

V : line valid

#### Data Cache Control register (DCCR)

Two fields have been added to the Data Cache control register:

| 4                   | 3                            | 1-2                                                                                                           | 0       |  |  |  |  |

|---------------------|------------------------------|---------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|

| _copy_back          | overtake_store               | lock                                                                                                          | enable  |  |  |  |  |

|                     |                              | —                                                                                                             | _enuble |  |  |  |  |

| DCCR_copy_back      | Enables the                  | copy back when set                                                                                            |         |  |  |  |  |

| DCCR_overtake_store |                              | allows missed cacheable loads to overtake pending stores<br>when the targeted addresses are not in conflict.  |         |  |  |  |  |

| DCCR_enable         | When set, th<br>after Reset) | When set, the Instruction Cache is enabled ( initialized at ( after Reset)                                    |         |  |  |  |  |

| DCCR_lock           | 0 : r<br>1 : t<br>2 : t      | ch banks are locked<br>to locked bank<br>bank 3 is locked<br>banks 3 and 2 are loc<br>banks 3,2 and 1 are loc | ked     |  |  |  |  |

|                     | Bank 0 is no                 | ot lockable.                                                                                                  |         |  |  |  |  |

Table 11.Data Cache Control register (DCCR)

#### **Data Cache Controller Address Space**

The Cache Tag registers, the LRU registers, and the Control register can be read or updated using regular Store instructions in Supervisor mode. The address given in operand should be formatted as follows :

Table 12.Data Cache Controller Address Decoding

| 31-18              | 17 | 16-15 | 14 | 13 | 12 | 11 | 10-4        | 3-2         | 1-0         |

|--------------------|----|-------|----|----|----|----|-------------|-------------|-------------|

| 11 001 000 000 000 | Op | Reg   | B3 | B2 | B1 | B0 | Line number | Word number | Byte number |

Bits 31-18 are the Data Cache Controller Base address, fixed as shown on the table.

The Op field tells if it is an update ("0") or a simple check ("1").In case of a check, the data value given in operand in the Store instruction will be compared to the checked register content and the operation will return a Bus Error if the values are different.

Reg shows which register is to be checked/updated :

- 00 : Control Reg

- 01 : Cache memory

- 10 : Cache Tag

- 11 : LRU register

B3..B0 : bank number (used for Cache Memory and Cache Tag. A "1" indicates that the corresponding bank is selected. Any combination is legal)

Line number : used for Cache Memory , LRU register and Cache Tag

Word number : for Cache Memory, indicates which word in the selected line is to be checked/updated Byte number : for partial store, indicates which byte of the word is to be checked/updated (Used for Cache Memory and the Cache Tag).

### **3.2 The 90C701 Core Bus**

The 90C701 core bus is the central link between the CPU core, memory, and peripherals. It can support high bandwidth (32-bit word per cycle, 200 MB/s), even in presence of wait states through a split cycle protocol. In other words a split cycle protocol allows interleaving accesses between all the bus agents, which can be CPU (caches), memory, or peripherals. Each transaction has an associated signature. All messages belonging to a transaction are sent with the associated signature. This core bus provides the right support for critical word first block transfers through out-of-order responses and word hint.

Other features include one cycle latency for bus acquisition through self-arbitration and a fast reaction time through self slave selection mechanisms.

Figure 6. Core bus interconnection

All these characteristics contribute to the performance of the SPARClet  $^{TM}$  90C701 processor, allowing one effective cycle per instruction even in presence of wait states due to the natural latency of memories and/or peripherals. The following figure shows how the 90C701 core bus interleaves device and memory accesses.

| Load queue in data cache  |          | data            |                    |             |           |        |        |  |

|---------------------------|----------|-----------------|--------------------|-------------|-----------|--------|--------|--|

| Fetch & decode unit       | Fetch in | nstruction from |                    | Inst 2      |           |        |        |  |

| Core bus transaction      |          | Addr Inst 1     | Addr data          | Addr Inst 2 | Inst 1    | data   | Inst 2 |  |

| Bus interface & memory    | ·        |                 | memory access memo |             | memory    | access |        |  |

| on-chip peripheral access |          | L               |                    | peripher    | al access |        |        |  |

Figure 7. Example of interleaved transactions on core bus

In this example SPARClet<sup>™</sup> is retrieving two instructions and one data in eight cycles. A regular RISC processor using traditional bus protocol will retrieve the two instructions and data in 16 cycles.

### 3.3 90C701 On-Chip Peripherals

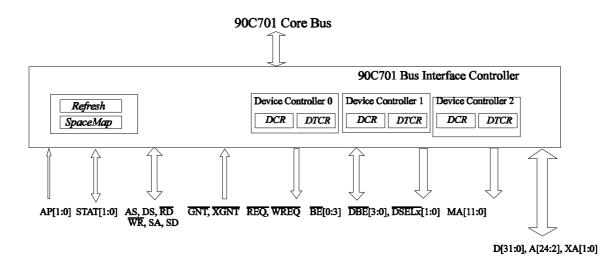

#### **3.3.1** Bus Interface Controller (BIC)

Figure 8. 90C701 Bus Interface Controller

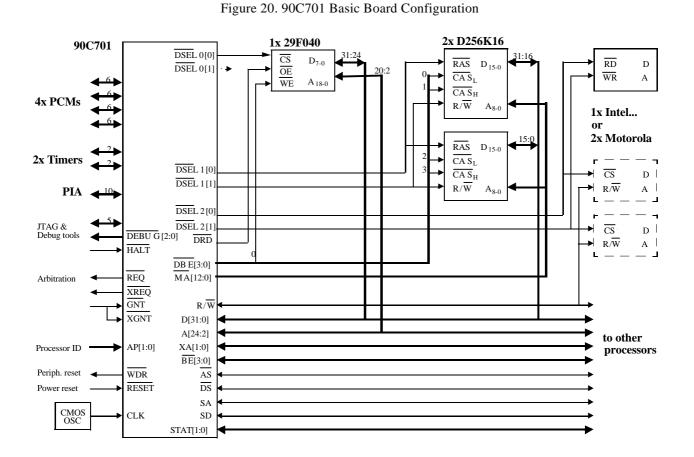

The 90C701 Bus Interface Controller (BIC) provides direct handling of DRAM, SRAM, and ROM memories as well as external I/O devices. The BIC features include :

- up to 256 MB accessing

- 48 MB directly controlled by the 90C701

- three independent device controllers (2 banks of 8 MB per device controller)

- No-multiplexed address/data bus

- 8/16/32 bit data accesses

- 8-bit boot access

- large scope of devices supported (SRAM, ROM, DRAM, FIFO, I/O couplers)

- Direct Memory Access supported

- CAS before RAS refresh for selected devices

- Self-refresh support

- User/supervisor address space mapping

- External clock synchronous

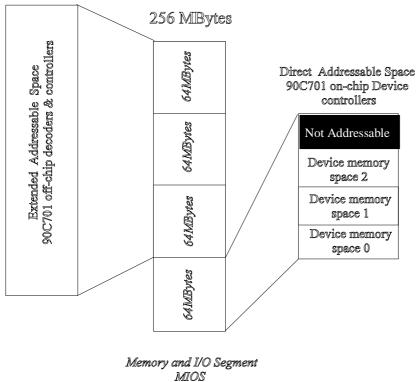

Within the 256-MB Memory and I/O addressable Space (MIOS), the Bus Interface Controller directly control 48-MB without external glue logic. This direct decoded area is included in one of the four 64-MB addressable memory pages.

The 48-MB direct address space is splitted into three segments of 16-MB. Three independent device controllers in the BIC are responsible for mapping memories and I/O devices within these segments.

# 90C701

(90C701 external address space)

Figure 9. Memory and I/O Addressing Space (MIOS)

Each device controller provides a pair of programmable chip selects and all share the byte enable control signals. The table below shows three possible configurations using the BIC.

| Device Controller | Device                   | Configuration       |  |  |

|-------------------|--------------------------|---------------------|--|--|

| 0                 | ROM                      | 2 banks of 8MB      |  |  |

| 1                 | DRAM                     | 2 banks of 8MB      |  |  |

| 2                 | Motorola type I/O device | 2 I/O devices       |  |  |

| 0                 | ROM, DRAM                | 1 bk DRAM, 1 bk ROM |  |  |

| 1                 | Intel type I/O device    | 1 I/O device        |  |  |

| 2                 | Motorola type I/O device | 2 I/O devices       |  |  |

| 0                 | ROM, SRAM                | 2 banks of 8MB      |  |  |

| 1                 | DRAM                     | 1 bk ROM, 1bk SRAM  |  |  |

| 2                 | Intel type I/O device    | 1 I/O devices       |  |  |

Table 13. Possible System Configurations

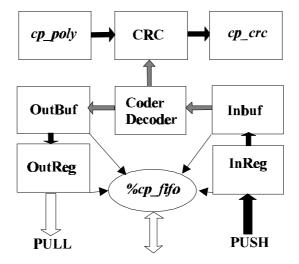

The waveform of the two signals (per device controller) is programmable. To control their timing, two BIC control registers per device controller, called DCR and DTCR, are available. The device control register (DCR) is dedicated to the general control of the device. The device timing control register (DTCR) contains timing information for the device accesses. The description of the register associated operations is provided in"Product Description" Chapter .

### 3.3.2 PCM/USART

**R**x/Tx lines On-chip peripherals bus value XBuffer TxControl **FxFifo** rat load pn Transmitter Tx Sequencer baud rate Receiver Rx Sequencer baud rate RxControl RxBuffer RxFifo

The PCM/USART module is software-configurable as a PCM or USART interface.

Figure 10.PCM/USART Block Diagram

When set up as a Universal Synchronous Asynchronous Receiver Transmitter (USART), each module features :

- 5- to 8-bit character length selection

- Parity bit option ( Even, Odd, One, Zero, No Parity )

- 1 or 2 stop bits (asynchronous mode)

- Break character detection

- Parity, overrun and framing error detection

- Internal/External Clock

- Receiver and Transceiver Fifos

- Theoritical Speed up to 8 Mb/s at 50MHz

Running as a PCM interface, coupled with the internal Communication coprocessor, it supports the HDLC or V110 protocols up to 8 Mbits/s (Full Duplex).

### **3.3.3** General Purpose Timer

This is a general purpose timer based on two 16-bit counters : the counter and the scaler. It can generate interrupts and external waveforms. The timer is triggered by external events or system clock. The timer is controlled by six registers: the Input Handler, the Scaler, the Scaler Reload Register, the Counter, the Counter Reload Register, and the Shaper. The Input Handler rules the external pins configuration: edge or level counting, active edge, etc. The Shaper allows the generation of programmable duty cycles, thus providing the PWM capability.

The Input Handler contains the attributes of the external counting events.

#### **3.3.4** OS Timers

This 32-bit decremental timer generates a trap at "0" detection. Depending on the Reload value, it can generate time reference intervals from one to  $2^{32}$  clock cycle (86 s at 50 MHz). It serves to support the Operating System task scheduling.

#### 3.3.5

The watchdog is an additional feature of the OsTimer, with a reduced functionality:

Load and Reset commands performed on the Counter Register will reload the watchdog while the Command Register content is discarded. The watchdog output signal has to be wired externally to the RESET\_ input (possibly through external circuitry) or also to the reset inputs of an external peripheral).

As we use a 32-bit decremental timer, the Watchdog duration can be tweaked up to  $2^{32}$  clock cycles. (86 s at 50 MHz)

#### **3.3.6** Peripheral Interface Adapter (PIA)

This cell allows the attributes of a single port pin to be programmed. This is done by using a dedicated command register which determines :

- if the port is input or output

- any filtering functions on the port (polarity, noise reduction, level or edge detection and masking) are ruled by the same Input Handler as the timer's one.

- the interrupt level associated to the port

So any PIA external pin can be used as an input, an output, or as an external hardware interrupt.

# **Chapter III**

# **Product Description**

## 4 90C701 Programming Model

### 4.1 SPARC Compliance

The SPARClet<sup>™</sup> architecture is compliant to SPARC V8<sup>1</sup>, and follows some of the recommendations proposed in SPARC V8 complement (the SPARC-V8 Embedded architecture specification)<sup>2</sup>.

#### **4.1.1** The 90C701 and the SPARC V8

SPARClet<sup>™</sup> implements the SPARC V8 architecture specification as described in the architecture manual. This means that SPARC compatibility is respected and any developed SPARC V8 tool is directly applicable to SPARClet<sup>™</sup>. Some SPARClet<sup>™</sup> implementation dependent features have been proposed in the 90C701, and those will be highlighted in this chapter.

In the following section an **[V8SID]** flag will refer to the V8 SPARClet <sup>TM</sup> Implementation Dependent features. For more details about the V8 architecture specifications refer to the official SPARC V8 manual.

#### 4.1.2 The 90C701 and the SPARC V8 Complement - SPARC V8E

The SPARC V8 complement (SPARC V8E) was released by SPARC International in 1994. The SPARC V8E has better performance than the SPARC V8 to support real-time and embedded applications. The V8E specification recommends implementation and architecture enhancements at several levels, such as instructions, real-time I/O, tracing, and emulation techniques.

The SPARClet<sup>TM</sup> architecture follows some of these recommendations. In the following section a **[V8E]** flag will refer to the SPARClet<sup>TM</sup> V8E features. For more details about the V8E architecture specifications refer to the official SPARC V8E release 1 document.

<sup>&</sup>lt;sup>1</sup> The SPARC Architecture Manual Version 8, SPARC International, Inc 535 Middlefield Road, Suite 210 Menlo Park, California 94025.

<sup>&</sup>lt;sup>2</sup> SPARC-V8 Embedded (V8E) Release 1 Architecture Specification.

## 4.2 Memory Organization

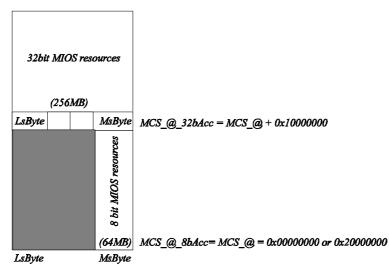

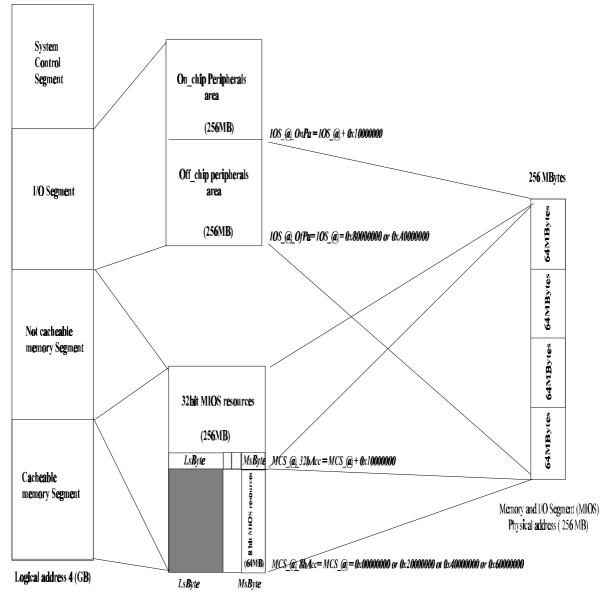

The 90C701 can access to a 4-GByte address space. 256-MB of the MIOS (decribed previously) are offered to support external devices such as ROM, SRAM, DRAM, and peripheral devices.

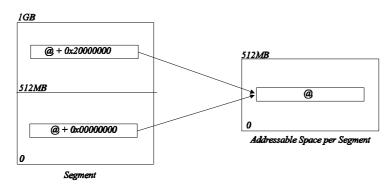

The 4-GByte addressing space is divided into four segments:

| Address                | Nam  | e Usage                      | Space |

|------------------------|------|------------------------------|-------|

| 0x3FFFFFFF-0x00000000  | CMS  | Cacheable Memory Segment     | 1 GB  |

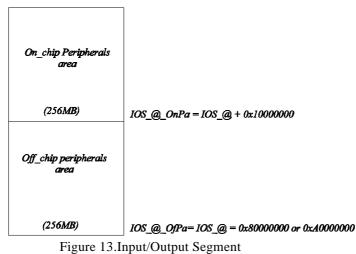

| 0x7FFFFFFF-0x40000000  | NCMS | Not Cacheable Memory Segment | 1 GB  |

| 0xBFFFFFFF-0x80000000  | IOS  | Input/Output Segment         | 1 GB  |

| 0xFFFFFFFFF-0xC0000000 | SCS  | System Control Segment       | 1 GB  |